### INTEGRATED CIRCUITS

Product specification

1998 Feb 10

IC17 Data Handbook

**SA639**

#### DESCRIPTION

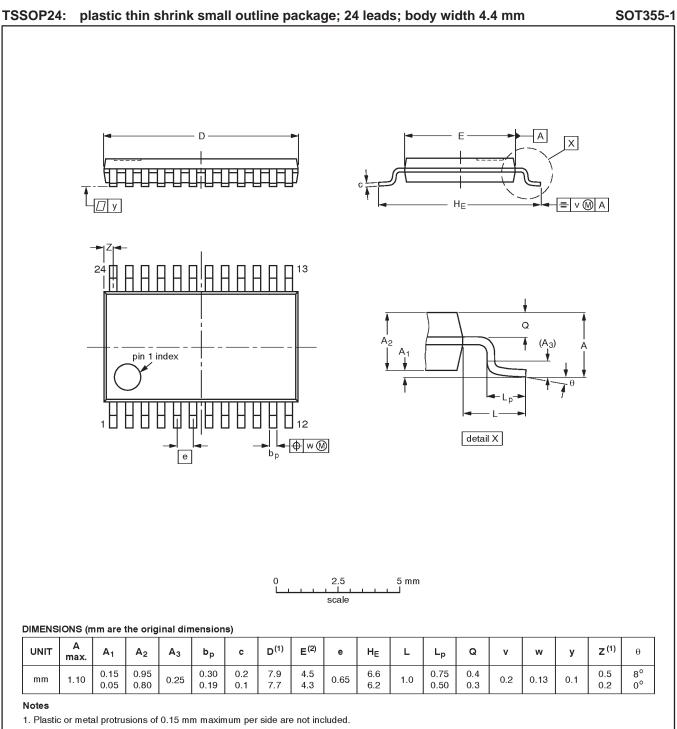

The SA639 is a low-voltage high performance monolithic FM IF system with high-speed RSSI incorporating a mixer/oscillator, two wideband limiting intermediate frequency amplifiers, quadrature detector, logarithmic received signal strength indicator (RSSI), fast RSSI op amps, voltage regulator, wideband data output, post detection filter amplifier and data switch. The SA639 is available in 24-lead TSSOP (Thin shrink small outline package).

The SA639 was designed for high bandwidth portable communication applications and will function down to 2.7V. The RF section is similar to the famous NE605. The data output provides a minimum bandwidth of 1MHz to demodulate wideband data. The RSSI output is amplified and has access to the feedback pin. This enables the designer to level adjust the outputs or add filtering.

The post-detection amplifier may be used to realize a low pass filter function. A programmable data switch routes a portion of the data signal to an external integration circuit that generates a data comparator reference voltage.

SA639 incorporates a power down mode which powers down the device when Pin 8 is high. Power down logic levels are CMOS and TTL compatible with high input impedance.

#### APPLICATIONS

- DECT (Digital European Cordless Telephone)

- FSK and ASK data receivers

#### FEATURES

- V<sub>CC</sub> = 2.7 to 5.5V

- Low power consumption: 8.6mA typ at 3V

- Wideband data output (1MHz min.)

- Fast RSSI rise and fall times

- Mixer input to >500MHz

- Mixer conversion power gain of 9.2dB and noise figure of 11dB at 110MHz

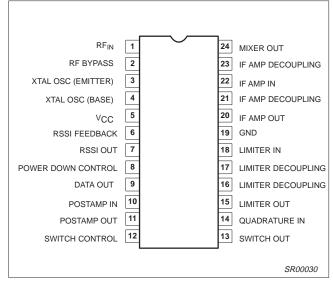

#### **PIN CONFIGURATION**

Figure 1. Pin Configuration

- XTAL oscillator effective to 150MHz (L.C. oscillator to 1GHz local oscillator can be injected)

- 92dB of IF Amp/Limiter power gain

- 25MHz limiter small signal bandwidth

- Temperature compensated logarithmic Received Signal Strength Indicator (RSSI) with a dynamic range in excess of 80dB

- RSSI output internal op amp

- Post detection amplifier for filtering

- Programmable data switch

- Excellent sensitivity:  $2.24\mu$ V into  $50\Omega$  matching network for 10dB SNR (Signal to Noise Ratio) with RF at 110MHz and IF at 9.8MHz

- ESD hardened

- Power down mode

#### **ORDERING INFORMATION**

| DESCRIPTION                                              | TEMPERATURE RANGE | ORDER CODE | DWG #   |

|----------------------------------------------------------|-------------------|------------|---------|

| 24-Pin Plastic TSSOP (Thin Shrink Small Outline Package) | -40 to +85°C      | SA639DH    | SOT-355 |

SA639

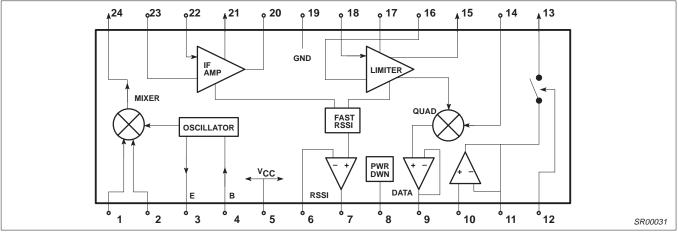

#### **BLOCK DIAGRAM**

Figure 2. Block Diagram

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL           | PARAMETER                                              | RATING                         | UNITS |

|------------------|--------------------------------------------------------|--------------------------------|-------|

| V <sub>CC</sub>  | Single supply voltage                                  | -0.3 to 6                      | V     |

| V <sub>IN</sub>  | Voltage applied to any other pin <sup>1</sup>          | -0.3 to (V <sub>CC</sub> +0.3) | V     |

| T <sub>STG</sub> | Storage temperature range                              | -65 to +150                    | °C    |

| T <sub>A</sub>   | Operating ambient temperature range SA639 <sup>2</sup> | -40 to +85                     | °C    |

NOTE:

1. Except logic input pins (Pins 8 and 12) which can have 6V maximum.

2.  $\theta_{JA}$  Thermal impedance (DH package) 117°C/W

### DC ELECTRICAL CHARACTERISTICS

$V_{CC}$  = +3V,  $T_A$  = 25°C; unless otherwise stated.

| SYMBOL           | PARAMETER                      | TEST CONDITIONS                |                     | _           | UNITS |             |                     |    |  |

|------------------|--------------------------------|--------------------------------|---------------------|-------------|-------|-------------|---------------------|----|--|

|                  |                                |                                | MIN                 | <b>-3</b> σ | TYP   | <b>+3</b> σ | MAX                 |    |  |

| V <sub>CC</sub>  | Power supply voltage range     |                                | 2.7                 |             | 3.0   |             | 5.5                 | V  |  |

| I <sub>CC</sub>  | DC current drain               | Pin 8 = LOW, Pin 12 = HIGH     |                     | 8.33        | 8.6   | 8.87        | 10                  | mA |  |

| I <sub>CC</sub>  | Standby                        | Pin 8 = HIGH, Pin 12 = HIGH    |                     | 131.9       | 140   | 148.1       | 500                 | μΑ |  |

|                  | Input ourrept                  | Pin 8 = LOW                    |                     |             |       |             | 10                  |    |  |

|                  | Input current                  | Pin 8 = HIGH                   |                     |             |       |             | 4                   | μA |  |

|                  | Lenged level                   | Pin 8 = LOW                    | 0                   |             |       |             | 0.3V <sub>CC</sub>  | V  |  |

|                  | Input level                    | Pin 8 = HIGH <sup>NO TAG</sup> | 0.7V <sub>CC</sub>  |             |       |             | 6                   |    |  |

| t <sub>ON</sub>  | Power up time                  | RSSI valid (10% to 90%)        |                     |             | 10    |             |                     | μs |  |

| t <sub>OFF</sub> | Power down time                | RSSI invalid (90% to 10%)      |                     |             | 5     |             |                     | μs |  |

|                  | Power up settling time         | Data output valid              |                     |             | 100   |             | 200                 | μs |  |

|                  | •                              | •                              | •                   |             |       |             |                     |    |  |

|                  | Switch closed                  | Pin 12 = LOW, PIN 8 = LOW      | 0                   |             |       |             | 0.3 V <sub>CC</sub> | V  |  |

|                  | Switch open (output tri-state) | Pin 12 = HIGH                  | 0.7 V <sub>CC</sub> |             |       |             | 6                   | V  |  |

|                  | land an and                    | Pin 12 = LOW                   |                     |             |       |             | 10                  |    |  |

|                  | Input current                  | Pin 12 = HIGH                  |                     |             |       |             | 4                   | μA |  |

|                  | Switch activation time         |                                |                     |             | 0.5   |             | 1                   | μs |  |

#### NOTE:

1. When the device is forced in power down mode via Pin 8, the Data Switch will output a voltage close to 1.6V and the state of the switch control input will have no effect.

SA639

#### AC ELECTRICAL CHARACTERISTICS

$T_A = 25^{\circ}$ C;  $V_{CC} = +3V$ , unless otherwise stated. RF frequency = 110.592MHz ;LO frequency = 120.392MHz; IF frequency = 9.8MHz; RF level = -45dBm; FM modulation = 576kHz with ±288kHz peak deviation, discriminator tank circuit Q=4. The parameters listed below are tested using automatic test equipment to assure consistent electrical characteristics. The limits do not represent the ultimate performance limits of the device. Use of an optimized RF layout will improve many of the listed parameters.

|                 |                                   |                                         | LIMITS<br>SA639 |             |      |             |      |                   |  |

|-----------------|-----------------------------------|-----------------------------------------|-----------------|-------------|------|-------------|------|-------------------|--|

| SYMBOL          | PARAMETER                         | TEST CONDITIONS                         |                 |             |      |             |      |                   |  |

|                 |                                   |                                         | MIN             | <b>-3</b> σ | TYP  | <b>+3</b> σ | MAX  |                   |  |

|                 | section (ext LO = -14dBm)         |                                         |                 |             |      |             |      |                   |  |

| f <sub>IN</sub> | Input signal frequency            |                                         |                 |             | 500  |             |      | MHz               |  |

| fosc            | External oscillator (buffer)      |                                         | 0.2             |             | 500  |             |      | MHz               |  |

|                 | Noise figure at 110MHz            |                                         |                 | 10.4        | 11   | 11.6        |      | dB                |  |

|                 | Third-order input intercept point | Matched f1=110.592MHz;<br>f2=110.852MHz |                 | -11         | -9.5 | -8          |      | dBm               |  |

|                 | Conversion power gain             |                                         | 6               | 8.6         | 9.2  | 11.1        |      | dB                |  |

|                 | RF input resistance               | Single-ended input                      |                 |             | 800  |             |      | Ω                 |  |

|                 | RF input capacitance              |                                         |                 |             | 3.5  |             |      | pF                |  |

|                 | Mixer output resistance           | (Pin 24)                                |                 |             | 330  |             |      | Ω                 |  |

| F section       | · · ·                             |                                         |                 |             |      |             |      |                   |  |

|                 | IF amp gain                       |                                         | 1               | 38.86       | 40   | 41.14       |      | dB                |  |

|                 | Limiter gain                      |                                         | 1               | 50.44       | 52   | 53.56       |      | dB                |  |

|                 | Input limiting -3dB               | Test at Pin 22                          | 1               |             | -100 |             |      | dBm               |  |

|                 | IF input impedance                |                                         |                 |             | 330  |             |      | Ω                 |  |

|                 | IF output impedance               |                                         |                 |             | 330  |             |      | Ω                 |  |

|                 | Limiter input impedance           |                                         |                 |             | 330  |             |      | Ω                 |  |

|                 | Limiter output impedance          |                                         |                 |             | 300  |             |      | Ω                 |  |

|                 | Limiter output level with no load |                                         |                 |             | 130  |             |      | mV <sub>RM</sub>  |  |

| RF/IF sect      | tion (ext LO = -14dBm)            |                                         |                 |             |      | 1           |      | -                 |  |

|                 | Data level                        | $R_{1} = 10k\Omega, C_{1} = 30pF$       | 260             |             | 360  | 1           |      | mV <sub>P-F</sub> |  |

|                 | Data bandwidth                    |                                         |                 | 2.1         | 2.4  | 2.7         |      | MHz               |  |

| S/N             | Signal-to-noise ratio             | No modulation for noise                 | 1               | 56.1        | 60   | 63.9        |      | dB                |  |

|                 | AM rejection                      | 80% AM 1kHz                             |                 | 34.8        | 36   | 37.2        |      | dB                |  |

|                 |                                   | RF level = -90dBm                       | 0               | 0.232       | 0.4  | 0.568       | 0.75 |                   |  |

|                 | RF RSSI output with buffer        | RF level = -45dBm                       | 0.5             | 0.732       | 0.9  | 1.068       | 1.3  |                   |  |

|                 |                                   | RF level = -10dBm                       | 0.8             | 1.032       | 1.2  | 1.368       | 1.6  | 1                 |  |

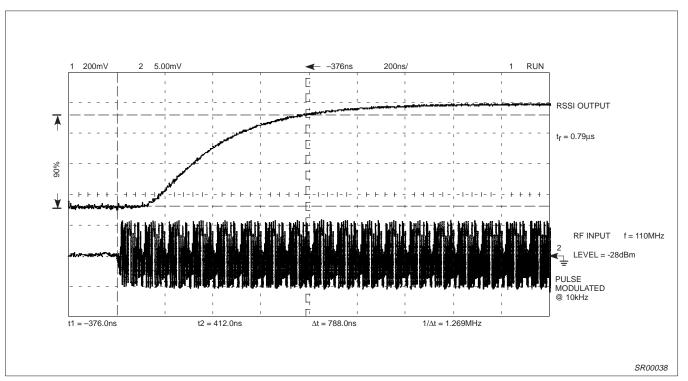

|                 | RF RSSI output rise time          | IF frequency = 9.8MHz                   |                 |             |      |             |      |                   |  |

|                 | (10kHz pulse, w/ 9.8MHz filter)   | RF level = -45dBm                       |                 |             | 0.8  |             |      |                   |  |

|                 | (no RSSI bypass capacitor)        | RF level = -28dBm                       |                 |             | 0.8  |             |      | μs                |  |

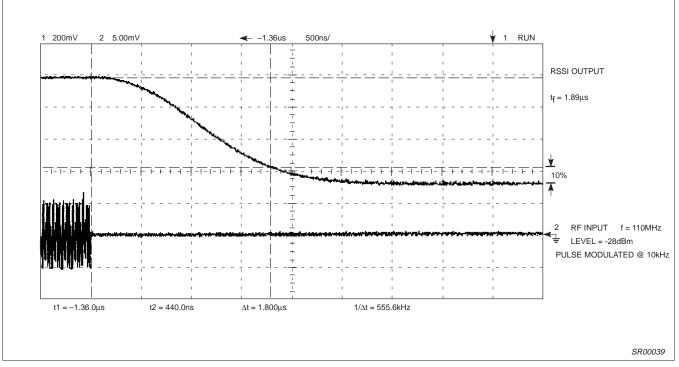

|                 | RF RSSI output fall time          | IF frequency = 9.8MHz                   |                 |             |      |             |      | -                 |  |

|                 | (10kHz pulse, w/ 9.8MHz filter)   | RF level = -45dBm                       |                 |             | 2.0  |             |      |                   |  |

|                 | (no RSSI bypass capacitor)        | RF level = -28dBm                       |                 |             | 1.8  |             |      | μs                |  |

|                 | RSSI range                        |                                         | 1               |             | 80   |             |      | dB                |  |

|                 | RSSI accuracy                     |                                         |                 |             | ±1.5 |             |      | dB                |  |

|                 | SINAD                             | RF level = -85dBm                       | 1               | 9.45        | 12   | 14.55       |      | dB                |  |

|                 | S/N                               | RF level = -100dBm                      |                 | 5.8         | 10   | 14.2        |      | dB                |  |

SA639

### AC ELECTRICAL CHARACTERISTICS (Continued)

|             |                                        |                                                                                                 | LIMITS |             |       |             |     |                   |  |

|-------------|----------------------------------------|-------------------------------------------------------------------------------------------------|--------|-------------|-------|-------------|-----|-------------------|--|

| SYMBOL      | PARAMETER                              | TEST CONDITIONS                                                                                 | SA639  |             |       |             |     |                   |  |

|             |                                        |                                                                                                 | MIN    | <b>-3</b> σ | TYP   | <b>+3</b> σ | MAX |                   |  |

| Post detec  | ction filter amplifier                 |                                                                                                 |        |             |       |             | -   |                   |  |

|             | Amplifier 3dB bandwidth                | AC coupled: $R_L = 10k\Omega$ ,<br>$C_L = 33pF$                                                 |        | 11.7        | 12.8  | 13.8        |     | MHz               |  |

|             | Amplifier gain                         | AC coupled: $R_L = 10k\Omega$ ,<br>$V_{OUT DC} = 1.6V$                                          |        |             | -0.2  |             |     | dB                |  |

|             | Slew rate                              | AC coupled: $R_L = 10k\Omega$ ,<br>$C_L = 33pF$                                                 |        |             | 2.4   |             |     | V/µs              |  |

|             | Input resistance                       |                                                                                                 | 300    |             |       |             |     | kΩ                |  |

|             | Input capacitance                      |                                                                                                 |        |             |       |             | 3   | pF                |  |

|             | Output impedance                       |                                                                                                 |        |             | 150   |             | 800 | Ω                 |  |

|             | Output load resistance                 | AC coupled                                                                                      | 5      |             |       |             |     | kΩ                |  |

|             | Output load capacitance <sup>1</sup>   | AC coupled                                                                                      |        |             | 30    |             |     | pF                |  |

|             | DC output level <sup>2</sup>           |                                                                                                 | 1.5    | 1.682       | 1.7   | 1.718       | 1.9 | V                 |  |

| Data swite  | :h                                     | -                                                                                               |        |             |       | •           |     |                   |  |

|             | DC input voltage range <sup>3</sup>    |                                                                                                 | 1.2    |             | 1.6   |             | 2.0 | V                 |  |

|             | AC input swing                         |                                                                                                 |        |             | 400   |             |     | mV <sub>P-P</sub> |  |

|             | Input impedance                        |                                                                                                 | 100    |             |       |             |     | kΩ                |  |

|             | Input capacitance                      |                                                                                                 |        |             |       |             | 5   | pF                |  |

|             | Output load resistance                 |                                                                                                 |        |             | 500   |             |     | Ω                 |  |

| Through N   | <b>lode</b> (Pin 12 = LOW)             | -                                                                                               |        |             |       |             |     |                   |  |

|             | AC voltage gain <sup>4</sup>           |                                                                                                 |        |             | -1.5  |             |     | dB                |  |

|             | Output drive capability                | Sink/source, V <sub>OUT DC</sub> = 1.6V                                                         | 3      |             |       |             |     | mA                |  |

|             | Slew rate                              | V <sub>OUT DC</sub> = 1.6V                                                                      |        |             | >14.0 |             |     | V/µs              |  |

|             | Static offset voltage <sup>5</sup>     | V <sub>IN DC</sub> = 1.2 to 2.0V                                                                |        | -0.6        | 0.30  | 1.2         | ±5  | mV                |  |

|             | Description for the large 2 fo         |                                                                                                 | -7     |             |       |             | +7  |                   |  |

|             | Dynamic offset voltage <sup>2, 6</sup> | V <sub>IN DC</sub> = 1.4 to 2.0V;<br>V <sub>CC</sub> = 3.0 to 5.0V;<br>RF level = -40 to -5 dBm | -10    |             |       |             | +10 | - mV              |  |

| Tri-State N | lode (Pin 12 = HIGH)                   |                                                                                                 |        |             |       |             |     |                   |  |

|             | Output leakage current                 | V <sub>OUT DC</sub> = 1.2 to 2.0V                                                               |        | 9.5         | 20    | 30.5        | 100 | nA                |  |

NOTES:

1. Includes filter feedback capacitance, comparator input capacitance. PCB stray capacitances and switch input capacitance.

2. Demodulator output DC coupled with Post Detection Filter Amplifier input and the demodulator tank exactly tuned to center frequency.

3. Includes DC offsets due to frequency offsets between Rx and Tx carrier and demodulator tank offset due to mis-tuning.

4. With a 400mV<sub>P-P</sub> sinusoid at 600kHz driving Pin 10. Output load resistance  $500\Omega$  in series with 10nF.

5. With a DC input and capacitor in the RC load fully charged.

7. Standard deviations are measured based on application of 60 parts.

<sup>6.</sup> The switch is closed every 10ms for a duration of 40µs. The DC offset is determined by calculating the difference of 2 DC measurements, which are determined as follows: 1) The first DC value is measured at the integrating capacitor of the switch when the switch is in the closed position immediately before it opens. The value to be measured is in the middle of the peak-to-peak excursion of the superimposed sine-wave. (DClow + (DChigh – DClow)/2). 2) The second DC value (calculated as above) is measured at Pin 11 immediately after the switch opens, and is the DC value which gives the largest DC offset to the first DC measurement within a 400µs DECT burst. Minimum and maximum limits are not tested, however, they are guaranteed by design and characterization using an optimized layout and application circuit.

### SA639

#### **CIRCUIT DESCRIPTION**

The SA639 is an IF signal processing system suitable for second IF or single conversion systems with input frequency as high as 1GHz. The bandwidth of the IF amplifier is about 40MHz, with 44dB(v) of gain from a 50 $\Omega$  source. The bandwidth of the limiter is about 28MHz with about 58dB(v) of gain from a 50 $\Omega$  source. However, the gain/bandwidth distribution is optimized for 9.8MHz, 330 $\Omega$  source applications. The overall system is well-suited to battery operation as well as high performance and high quality products of all types, such as digital cordless phones.

The input stage is a Gilbert cell mixer with oscillator. Typical mixer characteristics include a noise figure of 11dB, conversion power gain of 9.2dB, and input third-order intercept of -9.5dBm. The oscillator will operate in excess of 1GHz in L/C tank configurations. Hartley or Colpitts circuits can be used up to 100MHz for xtal configurations. Butler oscillators are recommended for xtal configurations up to 150MHz.

The output of the mixer is internally loaded with a 330 $\Omega$  resistor permitting direct connection to a 330 $\Omega$  ceramic filter. The input resistance of the limiting IF amplifiers is also 330 $\Omega$ . With most 330 $\Omega$  ceramic filters and many crystal filters, no impedance matching network is necessary. To achieve optimum linearity of the log signal strength indicator, there must be a 6dB(v) insertion loss between the first and second IF stages. If the IF filter or interstage network does not cause 6dB(v) insertion loss, a fixed or variable resistor can be added between the first IF output (Pin 20) and the interstage network.

The signal from the second limiting amplifier goes to a Gilbert cell quadrature detector. One port of the Gilbert cell is internally driven by the IF. The other output of the IF is AC-coupled to a tuned quadrature network. This signal, which now has a  $90^{\circ}$  phase relationship to the internal signal, drives the other port of the multiplier cell.

Overall, the IF section has a gain of 90dB. For operation at intermediate frequency at 9.8MHz. Special care must be given to layout, termination, and interstage loss to avoid instability.

The demodulated output (DATA) of the quadrature is a low impedance voltage output. This output is designed to handle a minimum bandwidth of 1MHz. This is designed to demodulate wideband data, such as in DECT applications.

#### **Post Detection Filter Amplifier**

The filter amplifier may be used to realize a group delay optimized low pass filter for post detection. The filter amplifier can be configured for Sallen & Key low pass with Bessel characteristic and a 3dB cut frequency of about 800kHz.

The filter amplifier provides a gain of 0dB. The output impedance is less than  $500\Omega$  in order to reduce frequency response changes as a result of amplifier load variations. The filter amplifier has a 3dB bandwidth of at least 4 MHz in order to keep the amplifier's

frequency response influence on the filter group delay characteristic at a minimum. At the center of the carrier it is mandatory to provide a filter output DC bias voltage of 1.6V in order to be within the input common mode range of the external data comparator. The filter output DC bias voltage specification holds for an exactly center tuned demodulator tank and for the demodulator output connected to the filter amplifier input.

#### **Data Switch**

The SA639 incorporates an active data switch used to derive the data comparator reference voltage by means of an external integration circuit. The data switch is typically closed for 10 $\mu$ s before and during reception of the synchronization word pattern, and is otherwise open. The external integration circuit is formed by an R/C low pass with a time constant of 5 to 10 $\mu$ s.

The active data switch provides excellent tracking behavior over a DC input range of 1.2 to 2.0V. For this range with an RC load (no static current drawn), the DC output voltage will not differ more than  $\pm$ 5mV from the input voltage. Since the active data switch is designed to behave like a non-linear charge pump (to allow fast tracking of the input signal without slew rate limitations under dynamic conditions of a 576kHz input signal with 400mV<sub>P-P</sub> and the RC load), the output signal will have a 340mV<sub>P-P</sub> output with a DC average that will not vary from the input DC average by more than  $\pm$ 10mV.

The data switch is able to sink/source 3mA from/to the external integration circuit in order to minimize the settling time after long power-down periods (DECT paging mode). In addition, during power-down conditions a reference voltage of approximately 1.6V will be used as the input to the switch. The switch will be in a low current mode to maintain the voltage on the external RC load. This will further reduce the settling time of the capacitor after power-up. It should be noted that during power-down the switch can only source and sink a trickle current (10 $\mu$ A). Thus, the user should make sure that other circuits (like the data comparator inputs) are not drawing current from the RC circuit.

The data switch provides a slew rate better than  $1V/\mu s$  in order to track with system DC offset from receive slot to receive slot (DECT idle lock or active mode). When the data switch is opened the output is in a tri-state mode with a leakage current of less than 100nA. This reduces discharge of the external integration circuit. When powered-down, the data switch will output a reference of approximately 1.6V to maintain a charge on the external RC circuit.

A Receive Signal Strength Indicator (RSSI) completes the circuitry. The output range is greater than 80dB and is temperature compensated. This log signal strength indicator exceeds the criteria for DECT cordless telephone. This signal drives an internal op amp. The op amp is capable of rail-to-rail output. It can be used for gain, filtering, or 2nd-order temperature compensation of the RSSI, if needed.

NOTE:  $dB(v) = 20log V_{OUT}/V_{IN}$

SA639

| PIN<br>No. | PIN<br>MNEMONIC |       |                                                                                           | PIN<br>No. | PIN<br>MNEMONIC   |       | EQUIVALENT CIRCUIT                  |

|------------|-----------------|-------|-------------------------------------------------------------------------------------------|------------|-------------------|-------|-------------------------------------|

| 1          | RF IN           | +1.07 | 0.8k 0.8k                                                                                 | 6          | RSSI<br>FEEDBACK  | +0.20 |                                     |

| 2          | RF<br>BYPASS    | +1.07 |                                                                                           | 7          | RSSI<br>OUT       | +0.20 |                                     |

| 3          | XTAL<br>OSC     | +1.57 |                                                                                           | 8          | POWER<br>DOWN     | 0.00  |                                     |

| 4          | XTAL<br>OSC     | +2.32 | <u>з</u><br><u>т</u><br><u>т</u><br><u>т</u><br><u>т</u><br>150µА<br><u>т</u><br><u>т</u> | 9          | DATA<br>OUT       | +1.7  |                                     |

| 5          | V <sub>CC</sub> | +3.00 | 5 VREF O<br>BANDGAP O                                                                     | 10         | POST<br>AMP<br>IN | +1.70 | 10<br>— 20µА<br>— 20µА<br>— SR00032 |

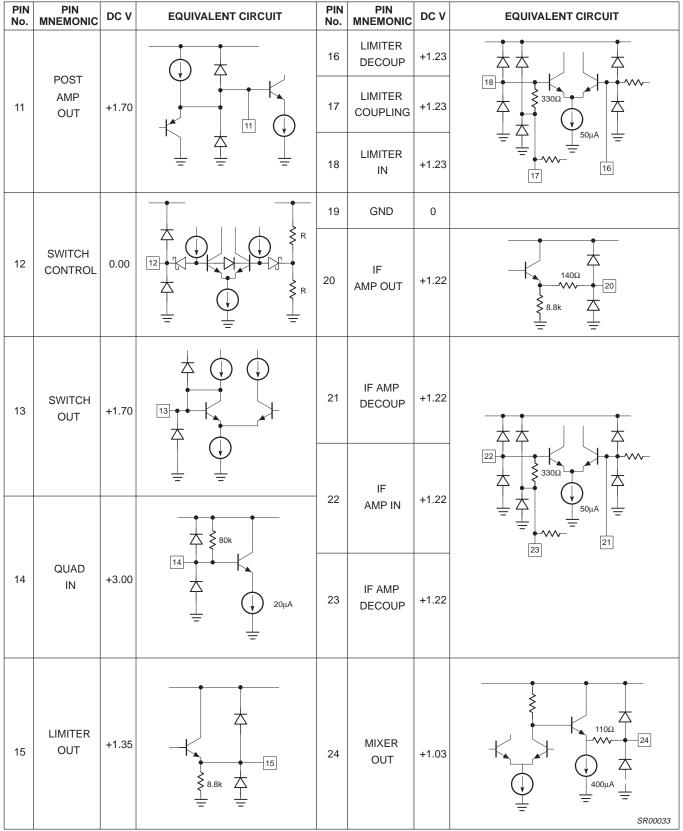

**PIN FUNCTIONS** All DC voltages measured with Pin 8 = Pin 12 = Pin 19 = 0V, Pin 5 = 3V and Pin 9 connected to Pin 10.

Figure 3. Pin Functions

SA639

**PIN FUNCTIONS** (continued)

Figure 4. Pin Functions (cont.)

SA639

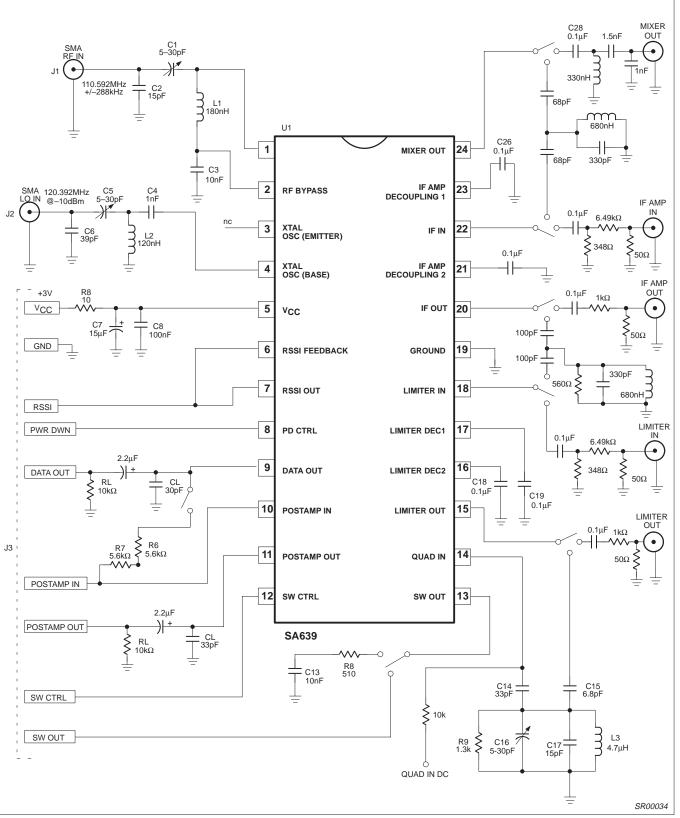

Figure 5. SA639 Test Circuit

SA639

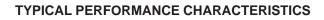

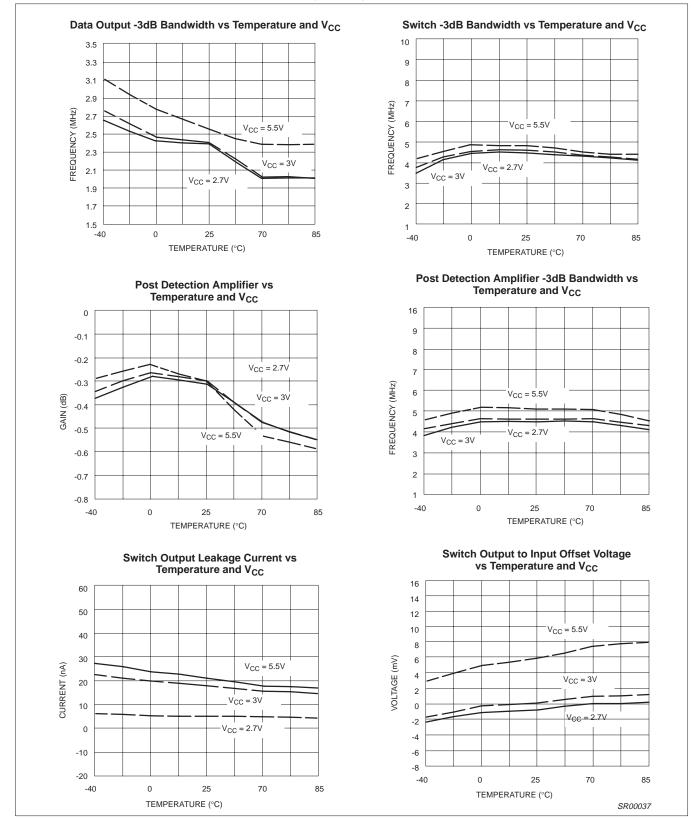

Figure 6. Typical Performance Characteristics

SA639

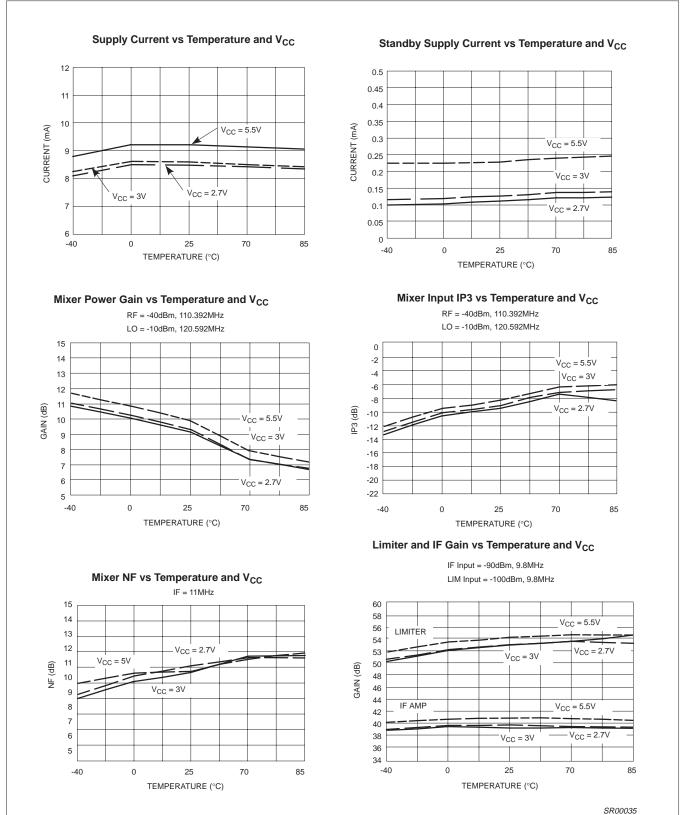

#### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Figure 7. Typical Performance Characteristics (cont.)

SA639

#### TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Figure 8. Typical Performance Characteristics (cont.)

Figure 9. SA639 RSSI Rise Time

Figure 10. SA639 RSSI Fall Time

1998 Feb 10

SA639

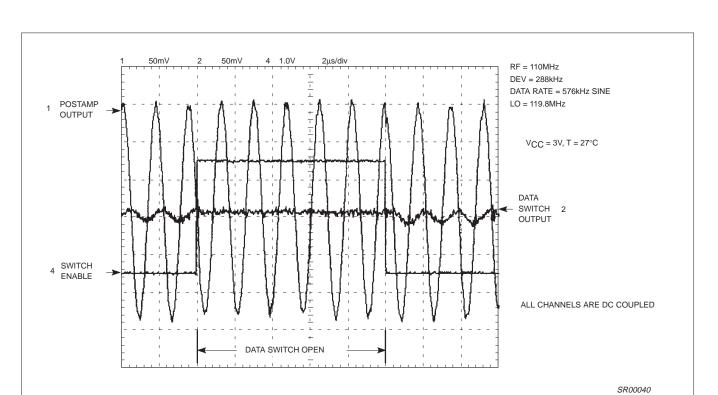

Figure 11. SA639 System Dynamic Response

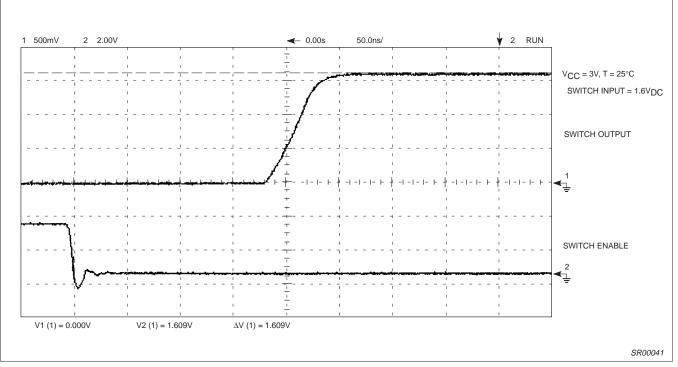

Figure 12. SA639 Data Switch Activation Time

SA639

SA639

Product specification

2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER    | REFERENCES EUROPEAN |  | ISSUE DATE |                                    |

|----------|-----|----------|---------------------|--|------------|------------------------------------|

| VERSION  | IEC | JEDEC    | EIAJ                |  | PROJECTION | ISSUE DATE                         |

| SOT355-1 |     | MO-153AD |                     |  |            | <del>- 93-06-16-</del><br>95-02-04 |

#### Data sheet status

| Data sheet<br>status      | Product<br>status | Definition [1]                                                                                                                                                                                                                                                  |

|---------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective specification   | Development       | This data sheet contains the design target or goal specifications for product development.<br>Specification may change in any manner without notice.                                                                                                            |

| Preliminary specification | Qualification     | This data sheet contains preliminary data, and supplementary data will be published at a later date.<br>Philips Semiconductors reserves the right to make chages at any time without notice in order to<br>improve design and supply the best possible product. |

| Product specification     | Production        | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                            |

[1] Please consult the most recently issued datasheet before initiating or completing a design.

#### Definitions

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

**Right to make changes** — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 1998 All rights reserved. Printed in U.S.A.

print code

Document order number:

Date of release: 2-98 9397 750 03301

Let's make things better.