# Serial-Input PLL Frequency Synthesizer

## Interfaces with Dual-Modulus Prescalers

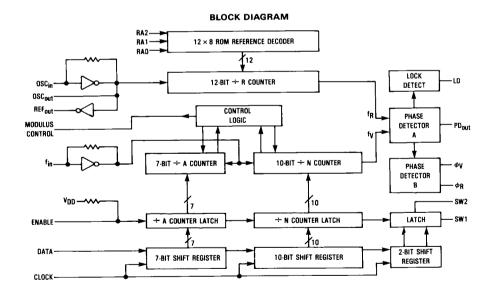

The MC145156-2 is programmed by a clocked, serial input, 19-bit data stream. The device features consist of a reference oscillator, selectable-reference divider, digital-phase detector, 10-bit programmable divide-by-N counter, 7-bit programmable divide-by-A counter, and the necessary shift register and latch circuitry for accepting serial input data.

The MC145156-2 is an improved-performance drop-in replacement for the MC145156-1. Power consumption has decreased and ESD and latch-up performance have improved.

- Low Power Consumption Through Use of CMOS Technology

- 3.0 to 9.0 V Supply Range

- On- or Off-Chip Reference Oscillator Operation with Buffered Output

- Compatible with the Serial Peripheral Interface (SPI) on CMOS MCUs

- Lock Detect Signal

- Two Open-Drain Switch Outputs

- Dual Modulus/Serial Programming

- 8 User-Selectable ÷ R Values: 8, 64, 128, 256, 640, 1000, 1024, 2048

- + N Range = 3 to 1023, + A Range = 0 to 127

- "Linearized" Digital Phase Detector Enhances Transfer Function Linearity

- Two Error Signal Options: Single Ended (Three-State) or Double Ended

- Chip Complexity: 6504 FETs or 1626 Equivalent Gates

## MC145156-2

MC145151-2 Series, Page 12

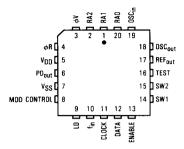

## PIN ASSIGNMENTS

PLASTIC DIP SOG PACKAGE

PLCC PACKAGE

## PIN DESCRIPTIONS

## **INPUTS**

## fin-Frequency Input

Input to the positive edge triggered  $\div$  N and  $\div$  A counters.  $f_{in}$  is typically derived from a dual-modulus prescaler and is ac coupled into the device. For larger amplitude signals (standard CMOS logic levels) dc coupling may be used.

## RAO, RA1, RA2-Reference Address inputs

These three inputs establish a code defining one of eight possible divide values for the total reference divider, as defined by the table below:

| Reference Address Code |     |     | Total<br>Divide |

|------------------------|-----|-----|-----------------|

| RA2                    | RA1 | RA0 | Value           |

| 0                      | 0   | 0   | 8               |

| 0                      | 0   | 1   | 64              |

| 0                      | 1   | 0   | 128             |

| 0                      | 1   | 1   | 256             |

| 1                      | 0   | 0   | 640             |

| 1                      | 0   | 1   | 1000            |

| 1                      | 1   | 0   | 1024            |

| 1                      | 1   | 1   | 2048            |

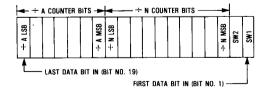

## CLOCK, DATA-Shift Clock, Serial Data Inputs

Shift register clock and data input. Each low-to-high transition clocks one bit into the on-chip 19-bit shift register. The Data input provides programming information for the 10-bit + N counter, the 7-bit + A counter, and the two switch signals SW1 and SW2. The entry format is as follows:

## **ENABLE**—Latch Enable Input

When high ("1") transfers contents of the shift register into the latches, and to the programmable counter inputs, and the switch outputs SW1 and SW2. When low ("0") inhibits the above action and thus allows changes to be made in the shift register data without affecting the counter programming and switch outputs. An on-chip pullup establishes a continuously high level for Enable when no external signal is applied. Enable is normally low and is pulsed high to transfer data to the latches.

## OSCin, OSCout-Reference Oscillator Input/Output

These pins form an on-chip reference oscillator when connected to terminals of an external parallel resonant crystal. Frequency setting capacitors of appropriate value must be connected from OSC<sub>in</sub> to ground and OSC<sub>out</sub> to ground. OSC<sub>in</sub> may also serve as input for an externally-generated reference signal. This signal is typically ac coupled to OSC<sub>in</sub>, but for larger amplitude signals (standard CMOS logic levels) dc coupling may also be used. In the external reference mode, no connection is required to OSC<sub>out</sub>.

## TEST-Factory Test Input

Used in manufacturing. Must be left open or tied to VSS.

## OUTPUTS

## PDout-Phase Detector A Output

Three state output of phase detector for use as loop error signal. Double-ended outputs are also available for this purpose (see  $\phi_V$  and  $\phi_R$ ).

Frequency fy>fR or fy Leading: Negative Pulses

Frequency fy < fR or fy Lagging: Positive Pulses

Frequency  $f_{\mbox{\scriptsize V}}=f_{\mbox{\scriptsize R}}$  and Phase Coincidence: High-Impedance State

## $\phi_V$ , $\phi_R$ --Phase Detector B Outputs

These phase detector outputs can be combined externally for a loop-error signal. A single-ended output is also available for this purpose (see  $PD_{Out}$ ).

If frequency fy is greater than fR or if the phase of fy is

MC145151-2 Series, Page 13

leading, then error information is provided by  $\phi_V$  pulsing low.  $\phi_R$  remains essentially high.

If the frequency  $f_V$  is less than  $f_R$  or if the phase of  $f_V$  is lagging, then error information is provided by  $\phi_R$  pulsing low.  $\phi_V$  remains essentially high.

If the frequency of  $f_V = f_R$  and both are in phase, then both  $\phi_V$  and  $\phi_R$  remain high except for a small minimum time period when both pulse low in phase.

## Modulus Control – Dual-Modulus Prescale Control Output

Signal generated by the on-chip control logic circuitry for controlling an external dual-modulus prescaler. The modulus control level will be low at the beginning of a count cycle and will remain low until the ÷ A counter has counted down from its programmed value. At this time, modulus control goes high and remains high until the ÷ N counter has counted the rest of the way down from its programmed value (N - A additional counts since both ÷ N and ÷ A are counting down during the first portion of the cycle). Modulus control is then set back low, the counters preset to their respective programmed values, and the above sequence repeated. This provides for a total programmable divide value  $(N_T) = N \cdot P + A$  where P and P+1 represent the dual-modulus prescaler divide values respectively for high and low modulus control levels. N the number programmed into the ÷ N counter, and A the number programmed into the + A counter.

## LD-Lock Detector Output

Lock detector signal. Essentially a high level when loop is locked ( $f_R$ ,  $f_V$  of same phase and frequency). Pulses low when loop is out of lock.

## SW1, SW2-Band Switch Outputs

SW1 and SW2 provide latched open-drain outputs corresponding to data bits numbers one and two. These outputs can be tied through external resistors to voltages as high as 15 V dc, independent of the V<sub>DD</sub> supply voltage. These are typically used for band switch functions. A logic one causes the output to assume a high-impedance state, while a logic zero causes the output to be low.

## REFout-Buffered Oscillator Output

Buffered output of on-chip reference oscillator or externally provided reference-input signal.

## **POWER SUPPLY**

## VDD

The positive power supply potential. This pin may range from +3 to +9 V with respect to  $V_{SS}$ .

#### Vss

The most negative supply potential. This pin is usually ground.

## **TYPICAL APPLICATIONS**

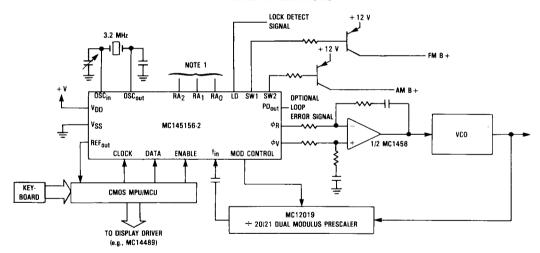

## NOTE 1

for AM: channel spacing = 5 kHz,  $\div$  R =  $\div$  640 (code 100) for FM: channel spacing = 25 kHz,  $\div$  R =  $\div$  128 (code 010)

AM/FM Radio Broadcast Synthesizer

MC145151-2 Series, Page 14

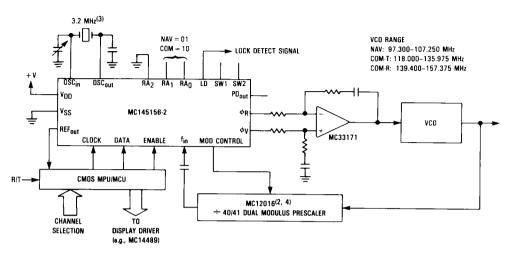

## NOTES:

- 1. For NAV:  $f_R = 50$  kHz,  $\div R = 64$  using 10.7 MHz lowside injection,  $N_{total} = 1946-2145$ . For COM-T:  $f_R = 25$  kHz,  $\div R = 128$ ,  $N_{total} = 4720-5439$ .

- For COM-R: f<sub>R</sub> = 25 kHz, + R = 128 using 21.4 MHz highside injection, N<sub>total</sub> = 5576-6295.

2. A ÷ 32/33 dual modulus approach is provided by substituting an MC12015 for the MC12016. The devices are pin equivalent.

- 3. A 6.4 MHz oscillator crystal can be used by selecting ÷ R = 128 (code 010) for NAV and ÷ R = 256 (code 011) for COM.

- 4. MC12013 + MC10131 combination may also be used to form the ÷ 40/41 prescaler.

**Avionics Navigation or Communication Synthesizer**